TC901

# MONOLITHIC, AUTO-ZEROED OPERATIONAL AMPLIFIER

## **FEATURES**

- Second-Generation Monolithic, Chopper-Stabilized Op Amp

- No External Capacitors Required

- Single-Supply Operation ..... ±15V or 5V to 32V

- Supply Current...... 450µA at 15V, Typ

- Input Offset Voltage ......7µV, Typ

- Common-Mode Rejection Ratio ......140dB, Typ

- Open-Loop Gain ..... 140dB Into 10k Load, Typ

- Input Noise ...... 5µV at 10Hz Bandwidth

- Pinout Compatible With ICL7650

- Lowest Parts Count Chopper Op Amp

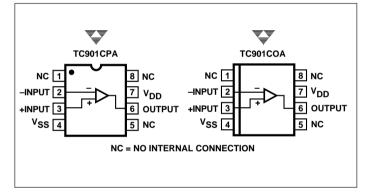

#### PIN CONFIGURATION (DIP and SOIC)

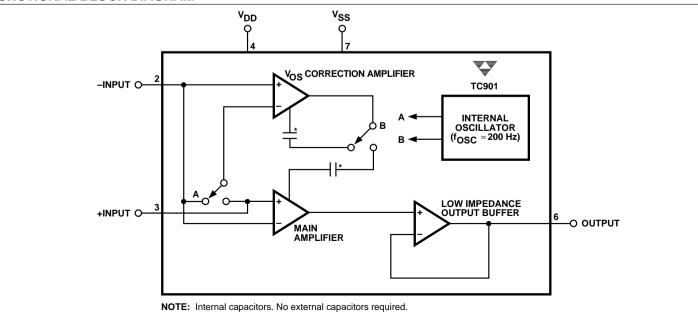

#### FUNCTIONAL BLOCK DIAGRAM

# **GENERAL DESCRIPTION**

The TC901 is a monolithic, auto-zeroed operational amplifier. It is a second-generation design of the TC91X CMOS chopper-stabilized op amps with on-chip capacitors.

Elimination of the external capacitors allows the designer to increase reliability, lower cost, and simplify design by lowering parts count.

Since the TC901 is an auto-zeroing op amp, input offset voltage is very low. More important, there is almost zero drift with time. This eliminates production line adjustments, as well as periodic calibration.

Notable electrical characteristics are low supply current (450 $\mu$ A, typical), single-supply operation (5V to 32V), low input offset voltage (7 $\mu$ V, typical), low noise (<5 $\mu$ V<sub>P-P</sub>, typical, for a 10Hz bandwidth), and fast recovery from saturation without the use of external clamp circuitry.

This device is supplied in 8-pin plastic DIP and plastic SOIC packages. It is pin compatible with bipolar, CMOS, JFET and other chopper-stabilized op amps using the industry-standard 741 pinout.

## **ORDERING INFORMATION**

| Part No. | Package           | Temperature<br>Range |  |  |

|----------|-------------------|----------------------|--|--|

| TC901COA | 8-Pin SOIC        | 0°C to +70°C         |  |  |

| TC901CPA | 8-Pin Plastic DIP | 0°C to +70°C         |  |  |

# **TC901**

## **ABSOLUTE MAXIMUM RATINGS\***

| Total Supply Voltage (V <sub>DD</sub> to V <sub>SS</sub> ) +36V |

|-----------------------------------------------------------------|

| Input Voltage $(V_{DD} + 0.3V)$ to $(V_{SS} - 0.3V)$            |

| Current Into Any Pin10mA                                        |

| While Operating100µA                                            |

| Storage Temperature Range 65°C to +150°C                        |

| Lead Temperature (Soldering, 10 sec)+300°C                      |

| Operating Temperature Range                                     |

| C Device0°C to +70°C                                            |

#### Package Power Dissipation ( $T_A = \le 70^{\circ}C$ )

| Plastic DIP  | 730mW |

|--------------|-------|

| Plastic SOIC | 470mW |

\*Static-sensitive device. Appropriate precautions should be taken when handling, shipping, or storing these devices. Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the devices. These are stress ratings only and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied.

| Symbol            | Parameter                                                     | Test Conditions                                                                                                                             | Min                 | Тур              | Max                  | Units             |

|-------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------|----------------------|-------------------|

| V <sub>OS</sub>   | Input Offset Voltage<br>(Figure 2)                            | $T_A = +25^{\circ}C$                                                                                                                        | _                   | 7                | 15                   | μV                |

| TCV <sub>OS</sub> | Average Temperature<br>Coefficient of Input<br>Offset Voltage | $0^{\circ}C \le T_A \le +70^{\circ}C$<br>(Note 1)                                                                                           | _                   | 0.05             | 0.15                 | μV/°C             |

| I <sub>BIAS</sub> | Average Input Bias<br>Current                                 | $\begin{array}{l} T_{A} = +25^{\circ}C \\ 0^{\circ}C \leq T_{A} \leq +70^{\circ}C \\ -25^{\circ}C \leq T_{A} \leq +85^{\circ}C \end{array}$ |                     | 30<br>0.2<br>0.2 | 50<br>10<br>10       | pA<br>nA<br>nA    |

| I <sub>OS</sub>   | Average Input<br>Offset Current                               | $T_A = +25^{\circ}C$ $T_A = +85^{\circ}C$                                                                                                   |                     | 50<br>—          | 100<br>1             | pA<br>nA          |

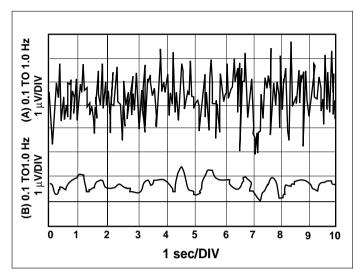

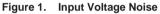

| e <sub>N</sub>    | Input Voltage Noise<br>(Figure 1B)                            | 0.1 to 1 Hz, $R_S \leq 100 \Omega$                                                                                                          | —                   | 1.2              | _                    | μV <sub>P-P</sub> |

| e <sub>N</sub>    | Input Voltage Noise<br>(Figure 1A)                            | 0.1 to 10 Hz, $R_S \! \leq \! 100 \Omega$                                                                                                   | —                   | 5                | _                    | μV <sub>P-P</sub> |

| CMRR              | Common-Mode Rejection<br>Ratio                                | $V_{SS} \le V_{CM} \le V_{DD} - 2V$                                                                                                         | 120                 | 140              | _                    | dB                |

| CMVR              | Common-Mode Voltage<br>Range                                  | $V_S = \pm 5V$ to $\pm 15V$                                                                                                                 | V <sub>SS</sub>     | —                | V <sub>DD</sub> –2   | V                 |

| A <sub>OL</sub>   | Open-Loop Voltage Gain                                        | $R_L = 10 \text{ k}\Omega, \text{ V}_S = \pm 15 \text{ V}$                                                                                  | 120                 | 140              | _                    | dB                |

| Vout              | Output Voltage Swing                                          | $R_L = 10 \text{ k}\Omega$                                                                                                                  | V <sub>SS</sub> + 1 | _                | V <sub>DD</sub> -1.2 | V                 |

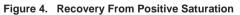

| BW                | Closed-Loop Bandwidth<br>(Figure 7)                           | Closed-Loop Gain = +1                                                                                                                       | _                   | 0.8              | —                    | MHz               |

| SR                | Slew Rate                                                     | $R_L = 10 \text{ kW}, C_L = 50 \text{ pF}$                                                                                                  |                     | 2                | _                    | V/µsec            |

| PSRR              | Power Supply Rejection Ratio                                  | $V_{\rm S} = \pm 5V$ to $\pm 15V$                                                                                                           | 120                 | 140              | _                    | dB                |

| V <sub>S</sub>    | Operating Supply Voltage<br>Range                             | Note 2                                                                                                                                      | ±3                  | -                | ±16                  | V                 |

| I <sub>S</sub>    | Quiescent Supply (Figure 2)                                   | $V_S = \pm 15V$                                                                                                                             | —                   | 0.45             | 0.6                  | mA                |

## **ELECTRICAL CHARACTERISTICS:** $V_S \pm 15V$ , $T_A = +25^{\circ}C$ , unless otherwise indicated.

NOTES: 1. Characterized; not 100% tested.

2. Single supply operation:  $V_{DD} = +5V$  to +32V.

#### **Overload Recovery**

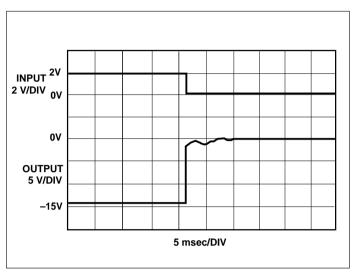

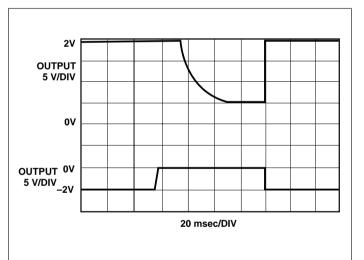

The TC901 recovers quickly from output saturation. Typical recovery time from positive output saturation is 20 msec. Negative output saturation recovery time is typically 5 msec.

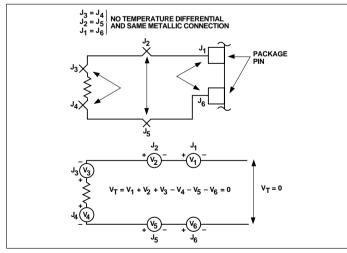

## **Thermocouple Errors**

Heating a junction made from two different metallic wires causes current flow. This is known as the Seebeck effect. An open-circuit voltage (Seebeck voltage) can be measured across the junction. Junction temperature and metal type determine the magnitude. Typical values are  $0.1 \mu V/^{\circ}C$  to  $10 \mu V/^{\circ}C$ . Thermal-induced voltages can be many times larger than the TC901's offset voltage drift. Unless unwanted thermocouple potentials can be controlled, system performance will be less than optimum.

Unwanted thermocouple junctions are created when leads are soldered or sockets/connectors are used. Low thermoelectric coefficient solder can reduce errors. A 60% Cd/40% Sn Pb solder has one-tenth the thermal voltage of common 64% Sn/36% Pb solder at a copper junction.

The number and type of dissimilar metallic junctions in the input circuit loop should be balanced. If the junctions are kept at the same temperature, their summation will add to zero, canceling errors (Figure 7).

Shielding precision analog circuits from air currents especially those caused by power dissipating components and fans — will minimize temperature gradients and minimize thermocouple-induced errors.

Figure 7. Unwanted Thermocouple Errors Eliminated by Reducing Thermal Gradients and Balancing Junctions

## **Avoiding Latch-Up**

Junction-isolated CMOS circuits inherently contain a parasitic p-n-p-n transistor circuit. Voltages exceeding the supplies by 0.3V should not be applied to the device pins.

Larger voltages can turn the p-n-p-n device on, causing excessive device power supply current and excessive power dissipation. TC901's power supply should be established at the same time (or before) input signals are applied. If this is not possible, input current should be limited to  $100\mu$ A to avoid triggering the p-n-p-n structure.

## **Pin Compatibility**

The CMOS TC901 is pin compatible with other chopperstabilized amplifiers, such as the 7650, 7652 and 1052. Amplifiers such as the 7650 require  $0.1\mu$ F external capacitors connected to pins 1 and 8. The TC901 includes the chopper capacitors on-chip, so external capacitors are not required. Since pins 1, 5 and 8 of the TC901 are not connected, the TC901 can directly replace other chopperstabilized amplifiers in existing circuits.

The TC901 pinout also matches many popular bipolar and JFET op amps, such as the OP-07, OP-20, LM101, LM108, 356 and 741. In many applications that operate from  $\pm$ 15V power supplies, the TC901 offers superior electrical performance and is a functional pin-compatible replacement. Offset voltage correction potentiometers, compensation capacitors, and chopper-stabilization capacitors can be removed when retrofitting existing equipment designs. System parts count, assembly time, and system cost are reduced, while reliability and performance are improved.

#### **Overload Recovery**

The TSC90X Series recovers quickly from output saturation. Typical recovery time from positive output saturation is 20 msec. Negative output saturation recovery time is typically 5 msec.

# MONOLITHIC, AUTO-ZEROED OPERATIONAL AMPLIFIER

# **TC901**

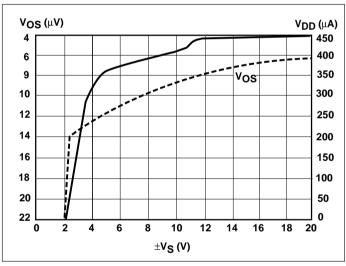

Figure 2. V<sub>OS</sub> and I<sub>DD</sub> vs Supply Voltage

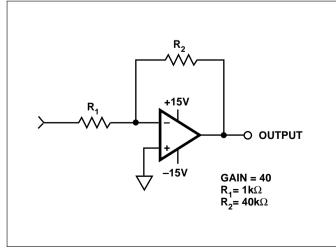

Figure 5. Saturation Test Circuit

Figure 3. Recovery From Negative Saturation

Figure 6. Phase-Gain